## University of California, Davis Society of Manufacturing Engineers at UC Davis

EEC 110A\*

**Electronics Circuits I**

Unofficial

## Mock Unofficial Practice Midterm Exam

\*Disclaimer: This document is a sample final exam of an Electronics Circuits I midterm. It is a mock exam and does not necessarily reflect the format—in the length of the exam, content covered, the protocol, and other aspects—of an actual midterm exam of EEC 110A in University of California, Davis. However, this covers multiple topics that seems to be a halfway agenda of EEC 110A and this document is an attempt to give students extra practice. The problems in this document are written entirely by the author. Any similarity, either in part or in whole, is a complete coincidence. If an error is caught, or if you have any questions and inquiries, please contact the author at mnhyu@ucdavis.edu.

A calculator is not encouraged where not needed. Scoring distribution for each question is not provided as it is not graded and discourages students from judging the importance of a topic over another. Please do not physically print out this document.

This examination has five (5) pages, including this front cover page and the end topology sheet.

**DO NOT share these documents outside of https://sme.ucdavis.edu.** Please do not distribute these to other websites, including Chegg, CourseHero, Discord, Quizlet, etc. All copyrights reserved by the author.

| Question 1) Diode Circuits              |  |

|-----------------------------------------|--|

| Question 2) Small Signal Model for BJTs |  |

| Question 3) Amplifier Topology          |  |

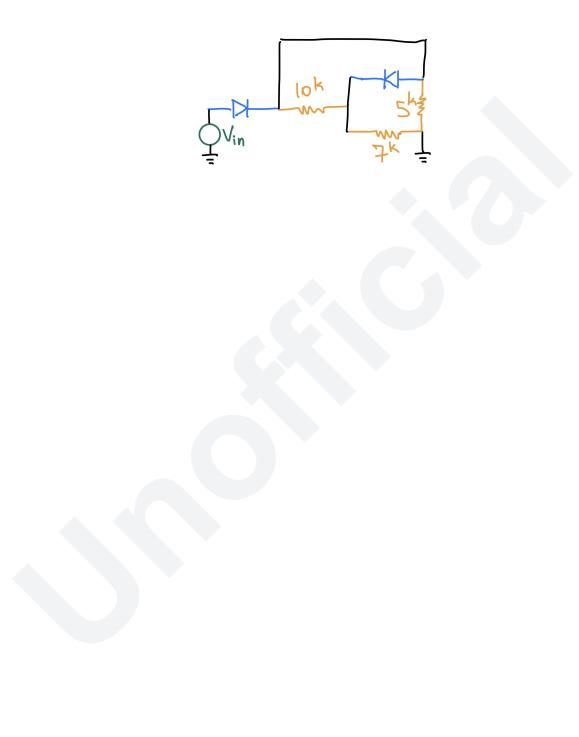

1) Plot  $P_{IN}$ , the power dissipated by  $V_{IN}$ , with respect to  $V_{IN}$  using the constant voltage model with  $V_{D,ON} = 1$ V. Label your graphs with units and important values.

By Man Yu <u>mnhyu@ucdavis.edu</u>. Do not print out a physical copy. Version 3 revised December 27, 2022 **DO NOT distribute this document. All copyrights reserved by the author.**

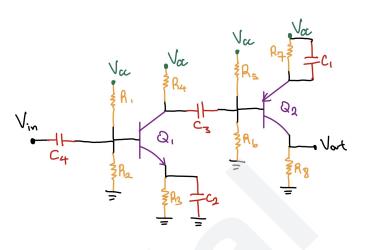

2) You are not allowed to use the topology formula sheet to solve this problem. Given the circuit below with 1 PNP BJT, 1 NPN BJT, 4 capacitors, and 8 resistors, and all transistors operate in the forward active region in the same temperature with  $V_A = \infty$ ,

- a) Find the transconductance of each BJT in terms of the resistor values, capacitor values,  $\beta_1$  (current gain of Q<sub>1</sub>),  $\beta_2$  (current gain of Q<sub>2</sub>),  $V_{BE}$  (for the NPN BJT),  $V_{EB}$  (for the PNP BJT),  $V_T$  (thermal voltage), and  $V_{CC}$ . Do not neglect base currents.

- b) Using the small signal model, find  $V_{OUT}/V_{IN}$  in terms of  $g_{m1}$ ,  $g_{m2}$ ,  $r_{\pi 1}$ ,  $r_{\pi 2}$ , and other resistor values in the circuit. You do not have to replace  $g_{m1}$  and  $g_{m2}$  with results from part a); instead, simply put  $g_{m1}$  and  $g_{m2}$ . Assume that all capacitors are large enough so that any AC signal would short them.

- c) Repeat part b), but instead of gain, find input resistance and output resistance (resistance looking into V<sub>IN</sub> and V<sub>OUT</sub>, respectively).

You could use the topology formula sheet to check your work for part b) and c).

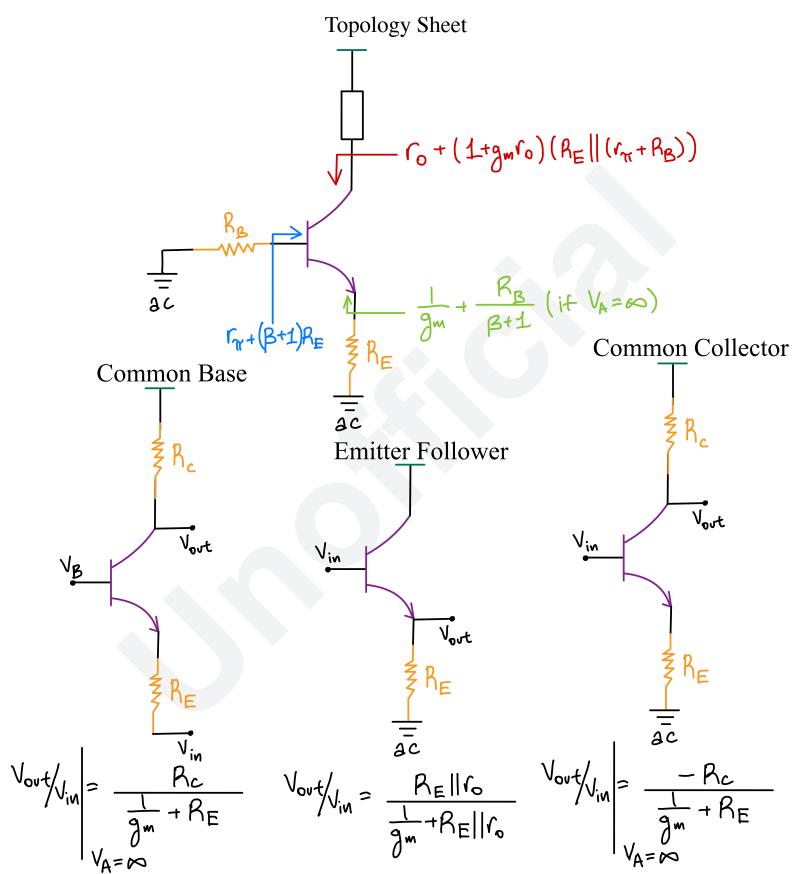

- 3) The saturation current of this BJT is  $10^{-16}$  A, current gain is 100, Early voltage is infinite, and thermal voltage is 26 mV. Using the topology formula sheet, find

- a)  $A_V = V_{OUT}/V_{IN}$ ,

- b) output resistance,  $R_{\text{OUT}}$ , the resistance looking into  $V_{\text{OUT}}$ , and

- c) input resistance,  $R_{IN}$ , the resistance looking into  $V_{IN}$ .

Do not neglect base currents.

By Man Yu <u>mnhyu@ucdavis.edu</u>. Do not print out a physical copy. Version 3 revised December 27, 2022 **DO NOT distribute this document. All copyrights reserved by the author.**

-Vort

1.8

By Man Yu <u>mnhyu@ucdavis.edu</u>. Do not print out a physical copy. Version 3 revised December 27, 2022 **DO NOT distribute this document. All copyrights reserved by the author.**