University of California, Davis Society of Manufacturing Engineers at UC Davis

EEC 110A\*

Electronics Circuits I

Unofficial

#### Mock Unofficial Practice Final Exam Solution

\*Disclaimer: This document is the solutions to a sample final exam of an Electronics Circuits I midterm. It is a mock exam and does not necessarily reflect the format—in the length of the exam, content covered, the protocol, and other aspects—of an actual final exam of EEC 110A in University of California, Davis. However, this covers multiple topics that seems to be a complete agenda of EEC 110A and this document is an attempt to give students extra practice. The problems in this document are written entirely by the author. Any similarity, either in part or in whole, is a complete coincidence. If an error is caught, or if you have any questions and inquiries, please contact the author at mnhyu@ucdavis.edu.

A calculator is not encouraged where not needed. Scoring distribution for each question is not provided as it discourages students from judging the importance of a topic over another.

This solution has fourteen (14) pages, including this front cover page and the topology sheet.

**DO NOT share these documents outside of https://sme.ucdavis.edu.** Please do not distribute these to other websites, including Chegg, CourseHero, Discord, Quizlet, etc. Please do not physically print out this document. All copyrights reserved by the author.

| Question 1) Short Response Questions                  |  |

|-------------------------------------------------------|--|

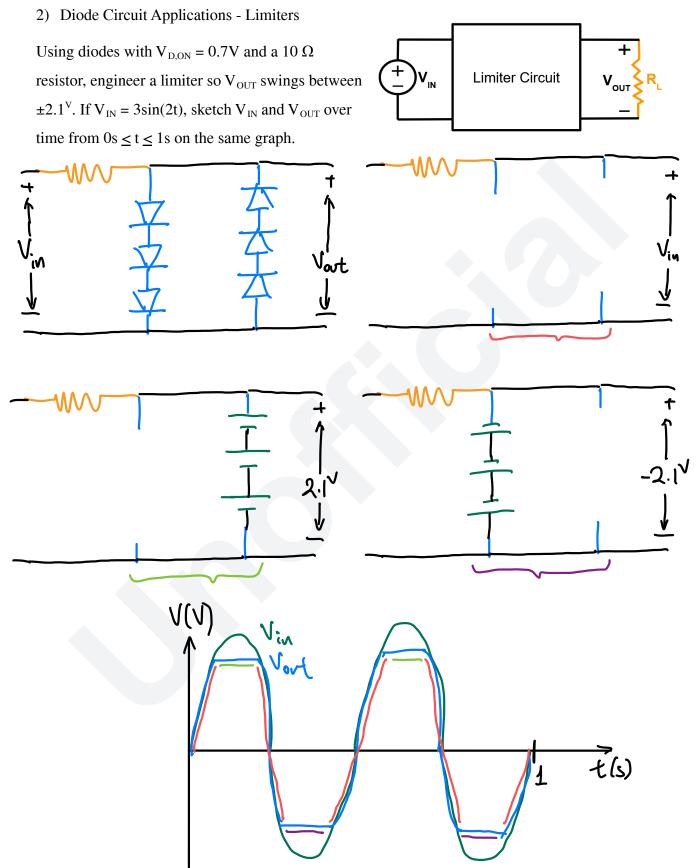

| Question 2) Diode Circuit Applications - Limiters     |  |

| Question 3) BJT Topology and Biasing                  |  |

| Question 4) Cascaded Amplifiers                       |  |

| Question 5) High Frequency Analysis of MOS Amplifiers |  |

| Question 6) Feedback                                  |  |

Note: Nodal  $V_{IN}$  in the schematics represent small signal AC inputs.

#### 1) Short Response Questions

Explain your claim for each in one sentence.

a) True or False: the unit for  $\mu_N C_{OX}(W/L)^* V_{TH}$  is  $\Omega$ , resistance.

$$I_{D} = \frac{1}{2} M_{A} Cox \frac{W}{L} (V_{as} - V_{ad})^{2}$$

$$[A] d \left\{ \mu_{A} Cox \frac{W_{3}}{L} [V]^{2} \right\}$$

$$[A] = \frac{1}{2} M_{A} Cox \frac{W_{3}}{L} [V]^{2}$$

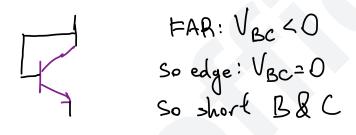

b) To "diode-connect" a BJT, what two terminals of a BJT should an engineer short together? Recall that diode-connecting a BJT directly puts the transistor at the edge of saturation.

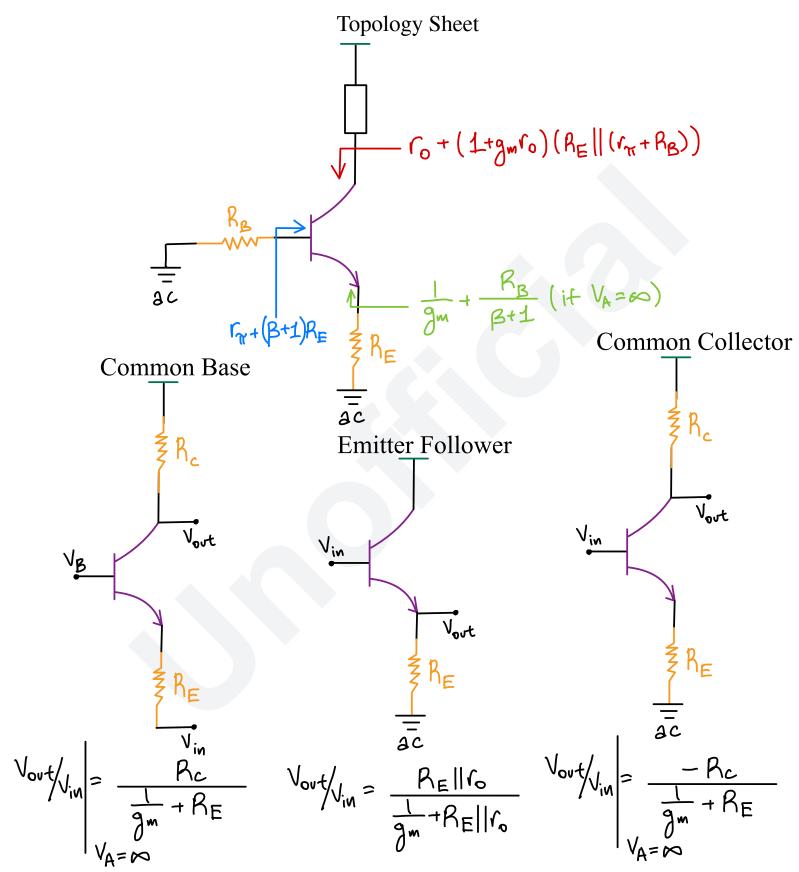

c) True or False: for an emitter follower, the absolute voltage gain is always less than or equal to one that is  $|A_{ij}| < 1$

$$|A_{v}| = \frac{R_{c}||R_{o}}{|g_{m} + R_{c}||R_{o}} < 1$$

$$\frac{R_{c}||R_{o}}{|g_{m} + R_{c}||R_{o}} < \frac{1}{g_{m}} + \frac{R_{c}||R_{o}}{|g_{m} + R_{c}||R_{o}}$$

$$\frac{R_{c}||R_{o}|}{|g_{m} + R_{c}||R_{o}} < \frac{1}{g_{m}} + \frac{R_{c}||R_{o}|}{|g_{m} + R_{c}||R_{o}|}$$

Also, EFs are not meant to be amplifiers, they are buffers. By Man Yu <u>mnhyu@ucdavis.edu</u>. Do not print out a physical copy. Version 1 created January 5, 2023 **DO NOT distribute this document.** All copyrights reserved by the author.

By Man Yu <u>mnhyu@ucdavis.edu</u>. Do not print out a physical copy. Version 1 created January 5, 2023 **DO NOT distribute this document. All copyrights reserved by the author.**

**10<sup>kΩ</sup>**

$\mathbf{V}_{\mathrm{out}}$

$V_{cc} = 7$

**100<sup>kΩ</sup>**

C<sub>B</sub>

3) BJT Topology and Biasing

The BJT here has  $V_{\rm A}$  = 5.722  $^{\rm V},$   $V_{\rm BE.ON}$  = 0.7V,  $\beta$  = 99.

- a) Find  $V_{Bias}$  so that the BJT is operating at the boundary of saturation and forward active region.

- b) Using your  $V_{Bias}$  from part a), find  $A_V = V_{OUT}/V_{IN}$ . Both capacitors are very large and short for AC signals.

$$V_{Bi} - R_{B} i_{B} - V_{BEON} - i_{B} (p+1)R_{E} = 0$$

$$V_{Bi} = i_{B} (R_{B} + (p+1)R_{B}) + V_{BEON}$$

$$= i_{B} (100^{h} + 100^{h}) + .7 = 200^{h} i_{B} + .7$$

$$P_{AR} i_{B} = (V_{Bi} - .7)/200^{h} (1)$$

$$V_{Bi} < 0$$

$$V_{Bc} < 0$$

$$V_{Bc} < 0$$

$$V_{Bc} = V_{Bi} - R_{B} i_{B} - (V_{cc} - R_{c} i_{B} S)$$

$$V_{c}$$

$$V_{bi} + i_{B} (R_{c} \beta - R_{B}) < V_{cc}$$

$$V_{bi} + \frac{(V_{Bi} - .7)}{200^{h}} (qa0 - 100)^{h} < 7$$

$$V_{Bi} \le 1.856^{V}, i_{C} \simeq 572.202 \mu A & \text{if } V_{T} = 25^{mV}, g_{m} = 22.888^{mD}$$

$$A_{V} = -g_{m} (R_{c} || \Gamma_{0}) = -22.8888^{mD} (10^{h} || \frac{5.922^{V}}{572.2\mu^{h}})$$

$$= -22.888^{mD} \times 5^{h.2}$$

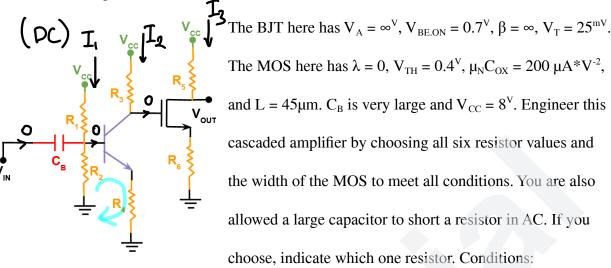

4) Cascaded Amplifiers

- $V_{OUT}/V_{IN} \ge 300.$

- $(W/L)_N$  should realistically be at least 20.

- To protect each transistor, neither stage should have an absolute gain of higher than 30.

- Maximum DC power consumption is 1 mW.

There are many possible ways to tackle this problem. This solution is one of the very many.

Let  $I_1$  be the current flowing through  $R_1$  and  $R_2$ . Taking the KVL of the far left branch in DC, and since we can neglect the base current of the BJT, we have a simple voltage divider.

$$I_{1} = \frac{V_{00}}{R_{1} + R_{2}} = \frac{8}{R_{1} + R_{2}}$$

We should decide  $R_1$  and  $R_2$  based on how much current we can have going through them. Since there are three DC currents in this circuit, let's assume that we would like a third the current budget for I<sub>1</sub>. We do not have to abide by this for the other two DC currents, but it is a good measure to decide the first two resistor values.

$$I_{1} V_{DD} \cong \frac{P_{bank}}{3} \rightarrow I_{1} \cong \frac{1^{mW}}{3 \cdot 8^{V}} \simeq \frac{8^{V}}{R_{1} + R_{a}}, \text{ so}$$

$$192^{k\Omega} \simeq R_{1} + R_{a} \qquad (1)$$

The voltage drop across  $R_2$  should be at least 700mV to accommodate for  $V_{BE,ON}$ . Let's be safe and have that voltage drop to be 800mV.

$$I_{1}R_{2} = 0.8^{V}$$

Since 0.8V is 10% of  $V_{CC}$ ,

$$\frac{R_2}{R_1 + R_2} = 0.1 (2)$$

To satisfy equation 1 and 2 simultaneously,  $R_1 = 172.8k\Omega$  and  $R_2 = 19.2k\Omega$ , and that also makes  $I_1 \approx 41.67 \mu A$ . Now, we should find the collector current (also the emitter current and let it be  $I_2$ ) to find the appropriate bias points for the BJT. Notice that we would have to choose  $R_4$ , so we have some freedom here as well. Per KVL around  $R_2$ ,  $V_{BE}$ , and  $R_4$ ,

$$I_{1}R_{2} = V_{BE} + I_{2}R_{4}$$

Assuming that the BJT is in the FAR (we will check this later),  $V_{BE} = 0.7V$ . Let's arbitrarily

choose  $R_4$  to be 10k $\Omega$ , which seems reasonable (but if it's not, we can change it later).

$$\frac{41.67\mu A(19.2ka) - 0.7}{10hq} = 10\mu A = I_2$$

We are allowed to have a gain of -30 in a given stage. Let's maximize that here. Using the BJT

stage is a common collector stage with a gain, we can determine  $\ensuremath{\mathsf{R}}_3$

$$-\frac{R_c}{V_{g_m} + R_E} = -\frac{R_3}{V_{g_mQ} + R_4} = \frac{-R_3}{25mV_{10_mA} + 10kQ} = -30$$

That makes  $R_3 = 375k\Omega$ . Now, to verify that we are in the forward active region, so all our

equations we have used are valid, we would want to make sure that  $V_{BC} < 0$ .

$$V_{BC} = V_{DD} \frac{R_2}{R_1 + R_2} - V_{DD} + R_3 I_2 < 0$$

8(0.1) - 8 + 375(0.01) = -3.45 < 0

Let's check our power budget so far.

$$P_{(1+2)} = V_{DD} (I_1 + I_2) = 8^{V} (41.67 \mu^{A} + 10^{\mu A}) = 413.33 \mu W$$

We still have 586.67  $\mu$ A left in our bank, so the drain current of the MOS would have to be at most 73.33  $\mu$ A. Remember, our goal now is to achieve at least -10 for the MOS stage to have an ultimate gain of 300. We should be cautious here, because it is harder to achieve a gain of larger than one if we have a common source with degeneration, so we should short out the degenerating resistor, R<sub>6</sub>, using a large capacitor. With that, our gain for stage 2 is now simply  $A_v = -g_{mM}R_s$  $g_{mN} = 2\mu_N C_{ov} + T_b$ . So we simply have to decide our size ratio and drain current from that. We have to make sure that the MOS is in saturation, and we should check to see what our limit is  $V_{GRO} < V_{T+T} \rightarrow V_{G-}V_D = 4.25 - (8 - T_D R_4) < 0.4$ , so

$I_{\rm p}R_{\rm s} < 4.15 \quad \textcircled{3}$  If we aim to have a gain of -10, then we can change the condition of equation 3 to not include R<sub>5</sub>.

$$-10 = -R_{\rm S} 2_{\rm Mn} C_{\rm Ox} I_{\rm O} \%, \qquad \frac{10\sqrt{I_{\rm O}}}{F_{\rm Mn} C_{\rm Ox} \%} < 4.15 \mbox{ }$$

With our maximum of  $I_D = 73.33 \ \mu$ A and minimum W/L = 20, equation 4 is satisfied regardless of what size and drain current we choose and we would remain in saturation. Let's choose a small  $I_D$  to minimize power usage, and  $I_D = 10 \ \mu$ A and W/L as a minimum of 20 (so W = 900 \mum), and pair this with a  $R_5 = 50k\Omega$ . This gives us a -14.14 gain, and the overall gain would be 424.3. We still need to find  $R_6$  that yields such drain current.  $T_D = \frac{1}{2} \ M_W C_{0X} \frac{W}{L} (V_{0X} - V_{TH})^2$  $10 = \frac{1}{2} \ 200 \times 20 (V_{0X} - 0.4)^R$  $V_{0X} \approx 470.7 \text{ mV}$  $V_{0X} \approx 470.7 \text{ mV}$  $V_{0X} \approx 100 \text{ m}^2 \text{$

And this gives us a gain of 424.3 and consumes 493.33 µW in DC.

V<sub>IN</sub>

$\mathbf{V}_{\mathsf{out}}$

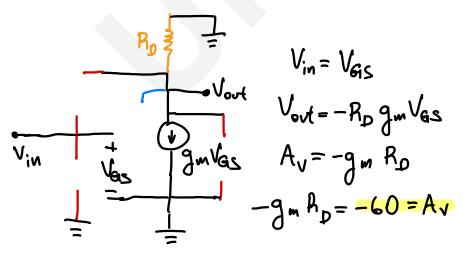

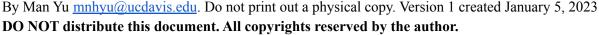

5) High Frequency Analysis of MOS Amplifiers

Given the amplifier below, where  $\lambda = 0$ ,  $V_{TH} = 0.4^{V}$ ,  $\mu_N C_{OX} = 400 \ \mu A^* V^{-2}$ , W/L = 30,  $V_{BIAS} = 0.5^{V}$ ,

$R_D = 50^{k\Omega}$ , and an L that (for part b and d) is super large so any AC signal will open circuit it,

- a) Find the drain current in DC.

- b) From the small signal model, find the low frequency gain  $V_{OUT}/V_{IN}$ .

- c) Using your gain from part b), find the exact output and input impedance

in terms of L,  $C_{GD}$ ,  $C_{DS}$ ,  $C_{GS}$ , and  $\omega$ . Do not open circuit the inductor.  $C_{GD} = 5FF$   $C_{GS} = 10FF$ d) Approximate the output pole frequency, if  $4C_{GD} = 2C_{GS} = C_{DS} = 20$  fF.

DC: (Lis short cht)

$$I_{D} = \frac{1}{2} \mu_{n} C_{0x} \frac{W}{L} (V_{GS} - V_{1H})^{2}$$

$$= \frac{1}{2} 400 \times 30 (0.5 - 0.4)^{8} = 60_{\mu} A^{2} I_{D}$$

$$= \frac{1}{2} 400 \times 30 (0.5 - 0.4)^{8} = 60_{\mu} A^{2} I_{D}$$

$$= \frac{1}{2} 400 \times 30 (0.5 - 0.4)^{8} = 60_{\mu} A^{2} I_{D}$$

$$= \frac{1}{2} 400 \times 30 (0.5 - 0.4)^{8} = 60_{\mu} A^{2} I_{D}$$

$$= \frac{1}{2} 400 \times 30 (0.5 - 0.4)^{8} = 60_{\mu} A^{2} I_{D}$$

gn= fun Cox  $\frac{\sqrt{2}}{L}$  Ip'=/2×400/4×30×60/4'= 1.2m2 AC: (L is open, free is lew enough to have small caps be open

By Man Yu <u>mnhyu@ucdavis.edu</u>. Do not print out a physical copy. Version 1 created January 5, 2023 **DO NOT distribute this document. All copyrights reserved by the author.**

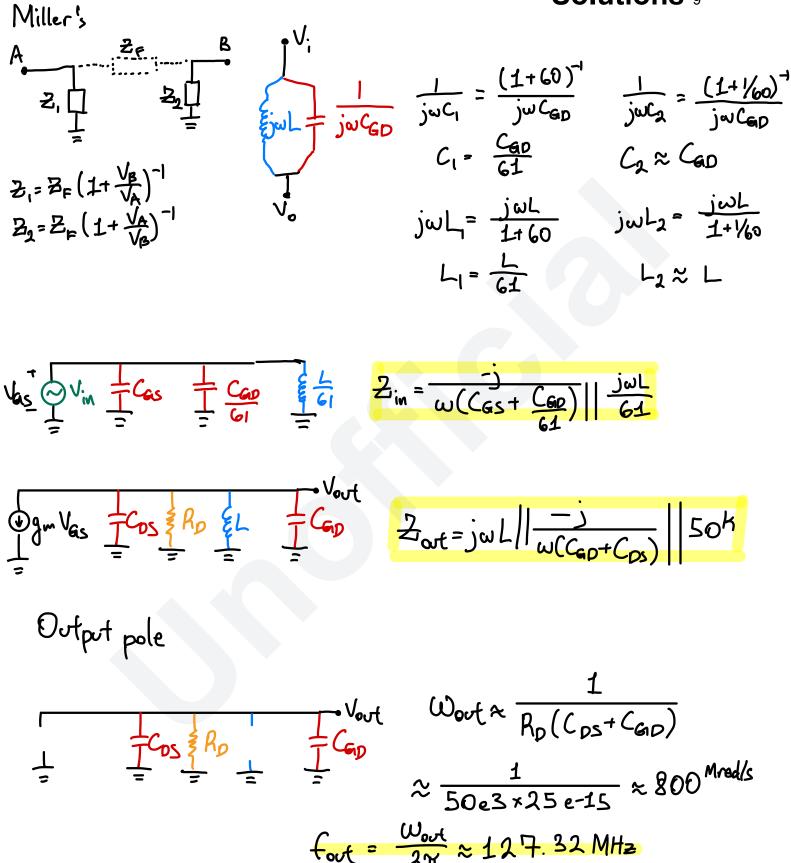

6) Feedback

For a negative feedback amplifier with forward gain of A and feedback gain of  $\beta$ ,

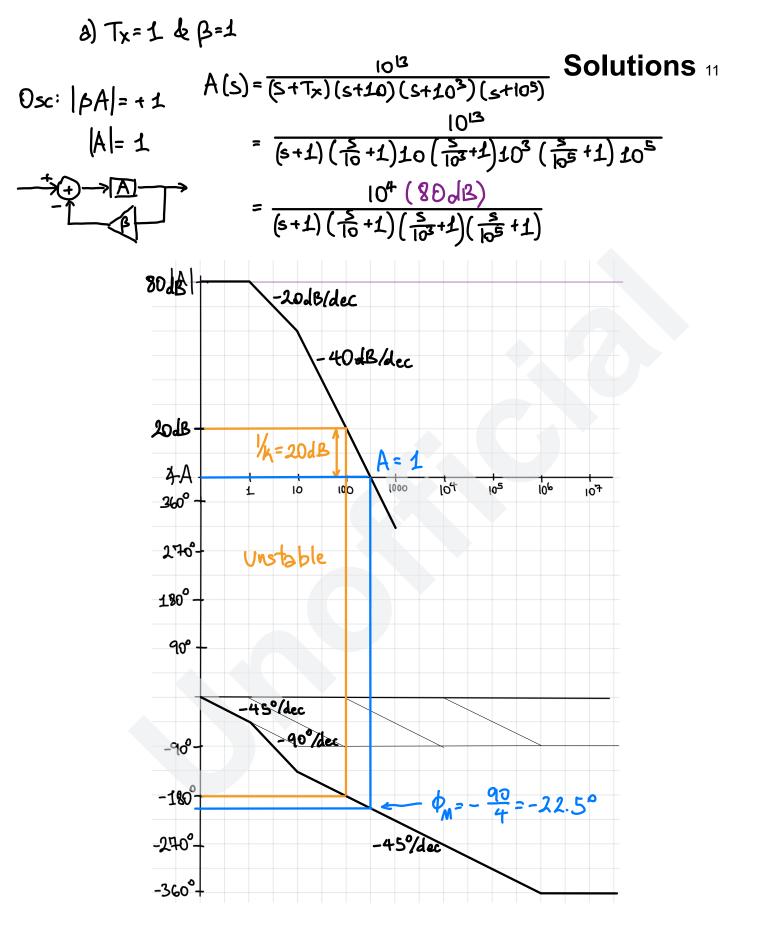

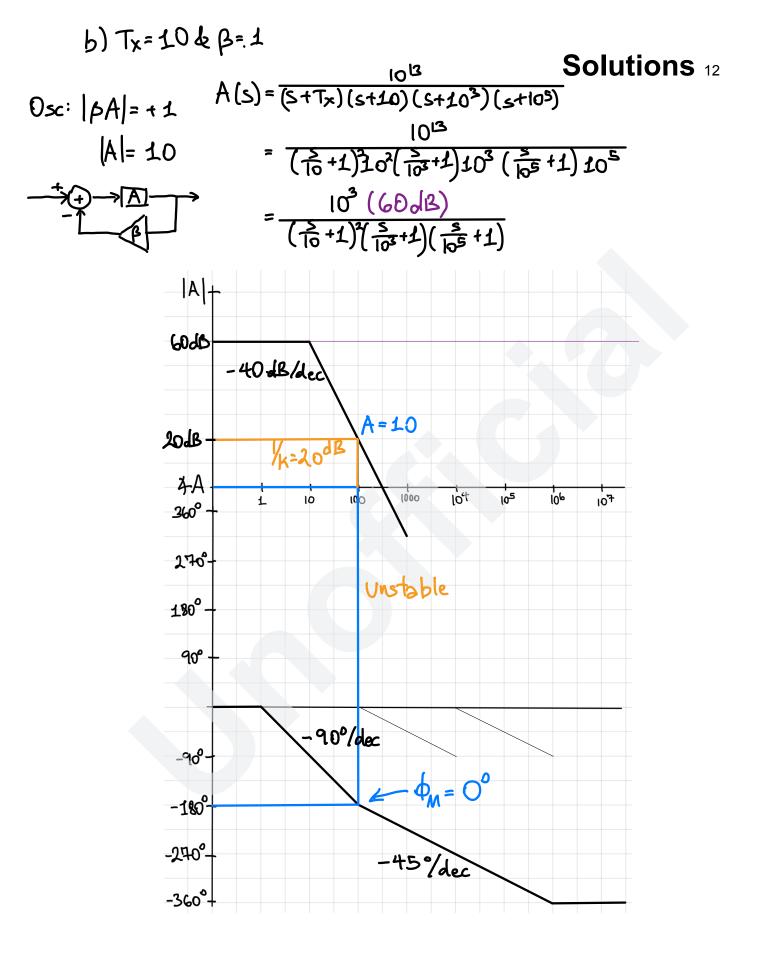

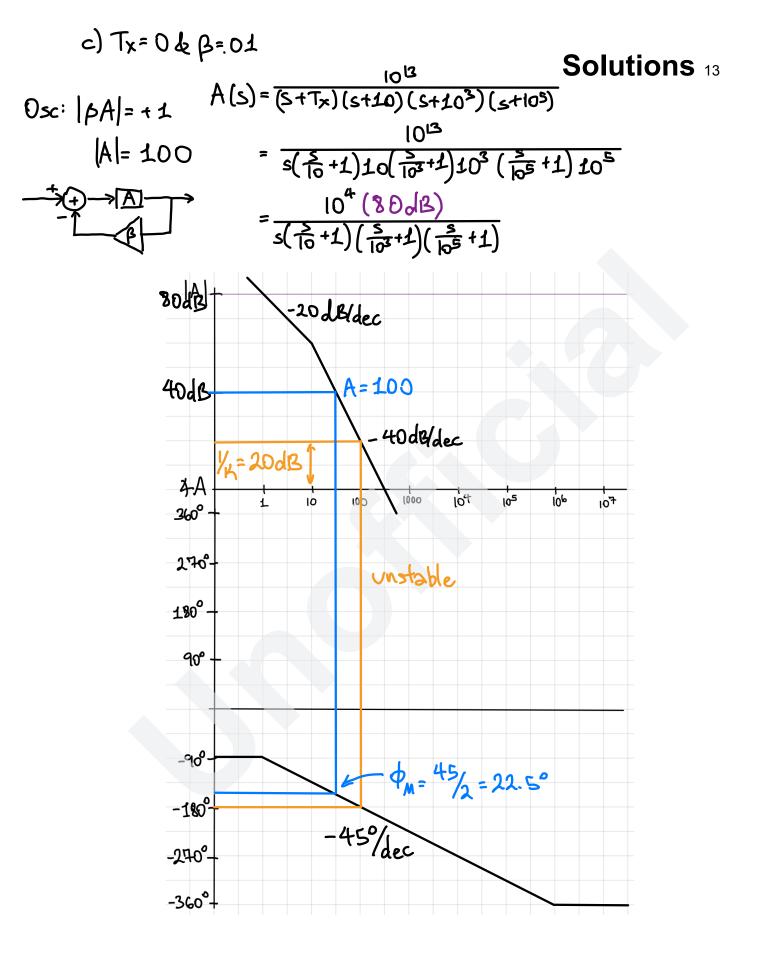

$$A(s) = \frac{10^{13}}{(s+T_{\chi})(s+10)(s+10^{3})(s+10^{5})}.$$

Find phase margin and comment on stability for each  $T_x$  and  $\beta$  combination below. If the open loop system is unstable, find an extra factor, K, of gain to A(s) so the open loop system oscillates.

|    | T <sub>X</sub> | β    | PM ( <sup>0</sup> ) - Stable? | Open Loop Stability | K (if applicable) |

|----|----------------|------|-------------------------------|---------------------|-------------------|

| a) | 1              | 1    | 22.5° unstable                | Unstable            | 0.1               |

| b) | 10             | 0.1  | 0° unstable                   | Unstable            | 0.1               |

| c) | 0              | 0.01 | 22.5° stable                  | Unstable            | 0.1               |

d) Given a general amplifier (not necessarily part a-c), complete the circuit using general

DO NOT distribute this document. All copyrights reserved by the author.

By Man Yu <u>mnhyu@ucdavis.edu</u>. Do not print out a physical copy. Version 1 created January 5, 2023 **DO NOT distribute this document. All copyrights reserved by the author.**

By Man Yu <u>mnhyu@ucdavis.edu</u>. Do not print out a physical copy. Version 1 created January 5, 2023 **DO NOT distribute this document. All copyrights reserved by the author.**

By Man Yu <u>mnhyu@ucdavis.edu</u>. Do not print out a physical copy. Version 1 created January 5, 2023 **DO NOT distribute this document. All copyrights reserved by the author.**